# Kilo-Qubit Scale Quantum Computer Design

DESIGN DOCUMENT

Team #24 Project for: Dr. Durga Paudyal, Ames Lab Advisors: Dr. Durga Paudyal, Dr. Jonathan Smith Team Members: Nicholas (Nick) Greenwood, Jacob Frieden, Samuel (Sam) Degnan, Arvid Gustafson, Chad (Colin) Gorgen, Emile Albert Kum Chi sdmay23-24@iastate.edu https://sdmay23-24.sd.ece.iastate.edu

Revised: April 29, 2023

# Academic and Professional Utilization

### Development Standards & Practices Used

- Waterfall Design Methodology (Development Practice)

- Waterfall Methodology is used because we do not have the knowledge to create many different sprints of designs and will need to put lots of knowledge into a final design.

- P1730 Standard for Quantum Computing Definitions (Development Standard)

- Through the development of this computer, we must communicate effectively. Adhering to standard definitions will be a must.

### Applicable Courses from Iowa State University Curriculum

- "PHYS 422X/522X: Foundations of Quantum Computing"

Highly relevant class, none of us have taken it

- "EE432/532: Micro-electronic fabrication Technique"

- Other PHYS courses

- General physics classes can contain useful information on basic, non-quantum physics

### Sources For New Skills/Knowledge Acquired (that was not taught in Iowa State University Curriculum)

- Quantum Computation and Quantum Information

- Textbook by Isaac Chuang and Michael Nielsen

- Microfabricated Ion Trap Junctions: 3D cross interchange\*

- Paper by Gavin Nop (TA)

- On Stabilizer Techniques and Their Application to Simulation and Certification of Quantum Devices

- Paper on Error Correction

- Honeywell Ion-Trap Quantum Computer Design Documentation/Review

- Presentation by Gavin Nop

- Computational Physics 4860

- University of Northern Iowa physics class

- Modern Physics 4100

- University of Northern Iowa physics class

- Modern Physics Lab 4110

- University of Northern Iowa physics class

- Various papers, lectures, virtual classes, and Youtube videos on ion traps, quantum computation, error correction, noise and other general quantum terminology and all associated topics discussed in this paper

### Table of Contents

| List of figures/tables/symbols/definitions                        | 3  |

|-------------------------------------------------------------------|----|

| 1 Team                                                            | 6  |

| 2 Introduction                                                    | 7  |

| 3 Project Plan                                                    | 9  |

| 3.1 Project Management/Tracking Procedures                        | 9  |

| 3.2 Task Decomposition                                            | 9  |

| 3.3 Project Proposed Milestones, Metrics, and Evaluation Criteria | 11 |

| 4 Design                                                          | 12 |

| 4.1 Design Context                                                | 13 |

| 4.1.1 Broader Context                                             | 13 |

| 4.1.2 Prior Work/Solutions                                        | 14 |

| 4.1.3 Technical Complexity                                        | 14 |

| 4.2 Design Exploration                                            | 15 |

| 4.2.1 Design Decisions                                            | 15 |

| 4.2.1.1 Design Decisions in CPRE 491                              | 15 |

| 4.2.1.2 Updates on Design Decisions in CPRE 492                   | 16 |

| 4.2.2. Ideation                                                   | 17 |

| 4.2.2.1 Ideation in CPRE 491                                      | 17 |

| 4.2.2.2 Updates on Ideation in CPRE 492                           | 18 |

| 4.2.3 Decision-Making and Trade-Off                               | 20 |

| 4.2.3.1 Decision-Making and Trade-Off in CPRE 491                 | 20 |

| 4.2.3.2 Decision-Making and Trade-Off in CPRE 492                 | 21 |

| 4.3 Proposed Design                                               | 22 |

| 4.3.1 Overview                                                    | 23 |

| 4.3.2 Detailed Design and Visual(s)                               | 24 |

| 4.3.3 Updates to Detailed Design and Visual(s)                    | 26 |

| Hardware Design:                                                  | 26 |

| Software Design:                                                  | 30 |

| 4.3.4 Past / Present Areas of Concern                             | 32 |

| Hardware                                                          | 32 |

| Software                                                          | 33 |

| 4.4 Technology Considerations                                     | 33 |

| 4.5 Updated Design Analysis                                       | 34 |

| 5 Testing and Security Concerns                                   | 34 |

| 5.1 Hardware Testing                                              | 34 |

| 5.3 Software Testing Process                                      | 35 |

| 5.4 Software Testing Results                                      | 35 |

| 5.5 Security Concerns                                             | 35 |

| 6 Closing Material                                | 35 |

|---------------------------------------------------|----|

| 6.1 Conclusion                                    | 35 |

| 6.2 Design Fitment in Quantum Computing Ecosystem | 36 |

| 6.3 References                                    | 37 |

| 7 Appendices                                      | 37 |

| 7.1 Operation Manual                              | 37 |

| 7.2 Code                                          | 40 |

|                                                   |    |

### List of figures/tables/symbols/definitions

#### - Superposition

Being a combination of both computational basis states (|o> and |1>)

#### - Entanglement

One qubit acts in a similar manner to another

#### - Quantum Fidelity

- Commonly used in quiskit; Represented by capital 'F'

- (bad) o <= F <= 1 (good)

- An example of 1.0 Fidelity would be finding that collapsing a positive state |+> would result in 50% collapse into 0 and 50% into 1, a perfect distribution

- If this collapse resulted in always os, that a F = 0.5

- Scales exponentially with # of qubits (2 qubits =  $2^2$  states)

- Basically a measure of how closely you can expect your qubit to behave irl compared to in quantum coding

- Essentially the link between "quantum coding" and actually quantum computing

- Fidelity < 1 is a result of noise

- $\langle \psi | A | \psi \rangle$  = Application of A to  $\psi$ , the basis which fidelity is determined off of

#### - Quantum Laws

- Superposition (see above)

- Clusters (Quantum and classical meanings)

- Set of computers that work together, as such can be viewed as a single system

- Each node performs the same task

- Deadlock

- Two applications are fighting for the same resource, they prevent the other from accessing it, and so both programs cease

- In single computers (ie nodes), deadlock is handled through algorithms and the OS, which means it probably isn't a big deal

#### - Nodes (Quantum and classical meanings)

- Each perform the same task in traditional (meaning should be easiest to implement)

- Each run their own OS

- Quantum Supremacy

- Exactly how it sounds: The goal / idea that a quantum computer can solve a (potentially useless) problem that a classical computer can't in any feasible amount of time

- Also known as "quantum advantage"

- Is expected to be done with "near-term" QCs, as the goal doesn't require high-quality error correction or the problem to be useful; no impact or hurdle of commercially viable QCs; primarily scientific

- Examples of potential problems:

- Shor's Algo for factoring integers prime factorization of an n-bit integer in  $O(n^3)$  time

- Boson sampling usage of boson scattering to evaluate expectation values of permanents of matrices

- Sampling an output distribution of a quantum circuit scales difficult exponentially with number of qubits

#### - Quantum Volume ("Area")

- Metric of capability for a quantum computer, introduced by IBM in 2019

- Maximum size of square quantum circuits that can be successfully implemented, is always a power of 2

- As of September 2022, Honeywell's H1 is king at QV 8192

- 13 square circuits

- Did this by implementing arbitrary angle two-qubit gates

- Honeywell has been increasing at a rate of 10x per year

#### - Arbitrary angle two-qubit gates

- Currently, researchers are working with single qubit gates of fully entangled two qubit gates. Arbitrary angle gates mean we can operate with two partially entangled gates

- Implemented by Honeywell in their Sept 2022 QV test

- Instead of having to fully entangle then walk back, can now just add a slight but of entanglement

- Very useful for fourier transform, where they can have ½ the number of arbitrary angle gates than traditional two qubit gates

#### Tables:

• Table 1: Ramifications of our project

#### Figures:

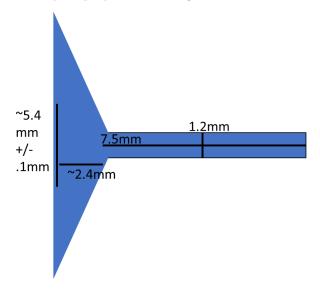

- Figure 1: Example of initial ion trap orientation

- Figure 2: A brief overview of the shape of our RF ion trap design

- Figure 3: Ions suspended above an ion trap

- Figure 4: Visualization of an ion handoff between two ion traps

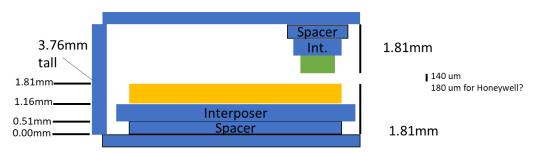

- Figure 5: A measurement-based schematic of a single HOA ion trap

- Figure 6: Side profile of the quantum computer

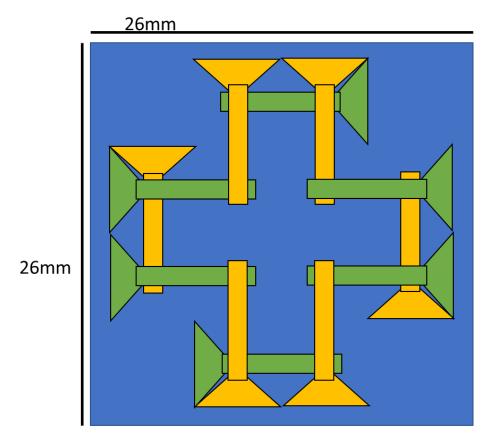

- Figure 7: A top-down view of the central quantum computer, with top chip removed for easy viewing

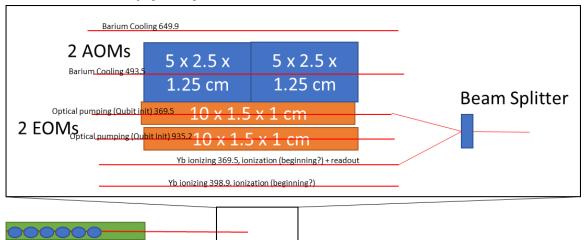

- Figure 8: A cutaway view of all lasers and ancillary components that will need to feed into the ion trap

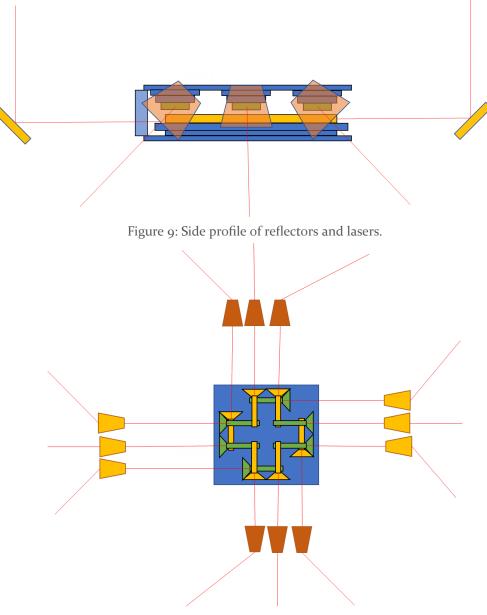

- Figure 9: Side profile of reflectors and lasers.

- Figure 10: Top-down view of reflectors and lasers.

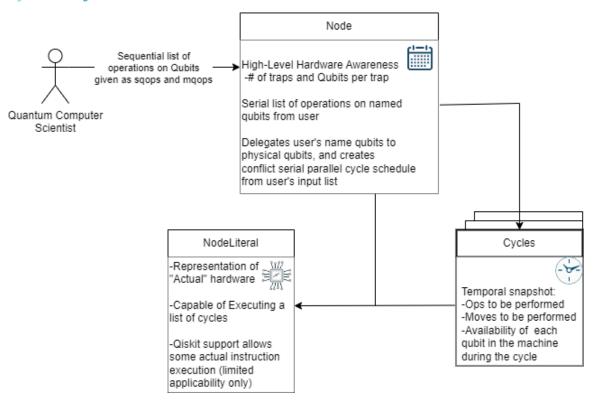

- Figure 11: UML-Like Diagram of The Digital Twin's Classes

- Figure 12: Example User Code

### 1 Team

The first section provides an overview of the team members, their majors, and the roles that each member had.

#### 1.1 TEAM MEMBERS

- Nicholas Greenwood Computer Engineering

- Jacob Frieden Software Engineering

- Sam Degnan Software Engineering

- Arvid Gustafson Software Engineering

- Colin Gorgen Electrical Engineering and Physics

- Emile Albert Kum Chi Electrical Engineering

#### 1.2 REQUIRED SKILL SETS FOR YOUR PROJECT

A basic understanding of quantum mechanics and a more thorough understanding of quantum computing are required. Knowledge in chip manufacturing techniques, coding techniques for simulation purposes, and robust capability of synthesizing technical writing were all paramount to the success of this project.

#### 1.3 PROJECT MANAGEMENT STYLE ADOPTED BY THE TEAM

We opted for a distributed management style. Nicholas is the contact point for communication between the team and the client / professors and the management of deadlines for documents and other pieces of senior design work. When work items are near due, Nicholas divides up the work evenly among team members.

For all non-senior design work (ie project based work), each team member undertakes their own assignment and sees that is completed to the clients standard. While assignments may overlap, this usually does not become apparent until the team meets again.

#### 1.4 PROJECT MANAGEMENT ROLES

- Nicholas Greenwood Administration and Integration, Hardware Team

- Jacob Frieden Administration and Research, Software Team

- Sam Degnan Requirements Synthesis and QC Error Correction expert, Software Team

- Arvid Gustafson Lead Developer and Coherence expert, Software Team

- Colin Gorgen Global Hardware Modeler, Hardware Team

- Emile Albert Kum Chi Electrical Design and QC electronics expert, Hardware Team

### 2 Introduction

In the introduction we address our problem statement, look at our intended uses and users in depth, and describe what sorts of requirements and constraints accompany our undertaking.

#### 2.1 PROBLEM STATEMENT

We will further the collective knowledge base of quantum computing and computer design by collectively <u>contributing to the design and construction of a working quantum computer</u> at <u>ISU/Ames Lab</u> over the <u>course of two semesters of senior design</u> This project will not conclude with us and will be carried on by <u>future</u> staff and students. We are doing so because quantum computing is a cutting edge technology, which offers opportunities to provide numerous advances in computational and scientific fields, and as a national lab and associated research university, Ames Lab and ISU's goals for furthering the state of science align with their construction of a quantum computer.

#### 2.2 INTENDED USERS AND USES

#### Ames Lab

- **Characteristics:** homogenous employment; heterogeneous expertise & explicit goals connected to their background, existing proposals/fundings, etc.; Highly technical individuals, likely interested in details and implementation as much as final product;

- **Needs:** Development of new techniques in the design of a quantum computer/proof of concept for existing techniques, verbose documentation/explanation of work

- **How They Use** / **Benefit:** They will be able to conduct research and forward the current knowledge base on quantum computer design and computing, increasing the productive potential and prestige of the institution.

#### Iowa State University students and faculty

- Characteristics: Large, diverse, and scholastic. A subset of students, likely in ECPE, Physics, ComSci, and related fields will be the most likely to be interested in this product. Within this subset, there are still wildly different areas of knowledge that will correspondingly result in different interests and concerns regarding our product. That said, they will all be technically inclined, though possibly to a lesser degree than the members of Ames Lab, and their access may be comparably limited.

- **Needs:** Access to quantum computing and/or quantum computer design starting at a possibly lower level of technical background than can be assumed of our other user base. This suggests the need for a full bodied "zero to hero" documentation structure.

- How They Use / Benefit: Involvement in the quantum computing domain increases the prestige of the university and the real value offered to its associates through access/exposure to the computer and its design. Students will have an expanded range of real world projects they can work on and take advantage of. Will utilize knowledge and any components for furthering of our goal or for new discoveries

#### State-of-the art researchers:

- **Characteristics:** Continuous drive for improvement, working on science projects. Very open and sharing for the benefit of everyone. Diverse ethnicities, cultural backgrounds, first-languages

- **Needs:** Perform high level calculations, Develop new solutions to current problems using new techniques and technologies developed by themselves or others

- **How They Use** / **Benefit:** Personal or group glory by using these concepts for further development in the field, enhanced knowledge in the field; Will utilize knowledge and any components for furthering of our goal or for new discoveries

#### 2.3 REQUIREMENTS & CONSTRAINTS

## Kilo-qubit (scale) Ytterbium Ion-Trap Quantum Computer (QC) Design Fundamental:

- Design a quantum computer that can be scaled to hold thousand(s) of qubits

- The design should utilize memory ion traps that preserve qubits for longer times (10s of machine cycles). These need to have transport access and be optical hardware addressable

- The design should also utilize computational ion-traps, which are the standard within current ion-trap QC designs.

#### **Resource:**

- Mike and Ike quantum physics book

- Honeywell Ion-Trap Quantum Computer Design Documentation/Review

- Papers, lectures, and virtual classes on ion traps and quantum computation

- 3D Modeling software (SolidWorks)

- Qiskit, a development kit for working with quantum circuits on quantum devices or simulations

- Quantum Computer design software

- A suitable word processor (Microsoft Office / G Suite) for documentation

#### Physical:

- The design of the QC must be of a reasonable size due temperature constraints associated with operating a quantum computer, all computational hardware must be able to fit within a space that could be cooled to 10 12 Kelvin.

- The QC design must be in line with the fabrication capabilities of Sandia[sic] labs, our design implementation collaborators

- QC must be capable of performing low-noise / interference ion transport along the trap.

- Note: Software based "transport" (swapping) mechanisms exist, but are impractically error-prone.

- Physical ion-transport is the standard, and minimal ion transport distance is prioritized to decrease error from noise exposure along the transport channel.

#### Economic / Market:

- There are no economic requirements

- There may be economic constraints

- The ability to produce QC-level components is not one that Iowa State possesses

- We would need to utilize outside labor and outside funding to physically build any components

- Labor in the form of Sandia[sic] labs, our design partner

- Any future construction of the outlined design would require significant funding in the form of grants or private backing

#### Software:

- Software requirements

- We must be able to run quantum circuits accurately

- We must be able to schedule qubits

- Quantum resources must be used appropriately, for example you cannot run multiple gates on a qubit in one cycle

- We must be able to scale the size of the digital twin

- Software constraints

- Use of ion computer backgrounds in software costs money

- We do not actually have a quantum computer and can only simulate it

- We do not have enough time to implement many of the software requirements

#### Other:

- As is customary in any field of advanced science, an advancement such as ours must be outlined in an academically reviewed paper.

### 3 Project Plan

Our Project Plan outlines how we completed and tracked our work, decomposes our tasks into actionable steps, and laid out benchmarks / milestones that we achieved and ones that we see as viable going forward.

#### 3.1 PROJECT MANAGEMENT/TRACKING PROCEDURES

Due to the large amount of knowledge that we needed to build up, we chose to use a waterfall project management approach. Creating a viable product iteration simply isn't possible within a small portion of time such as a sprint. The requirements of a quantum computer have been well established since the project began. Due to this being a largely physical design (in concept) of this Quantum Computer (QC), the iteration of designs cam in continued implementation of features into an overall computer design, as opposed to doing full minimum viable product (MVPs) and iterating on each one.

We used GroupMe for communication and sharing knowledge amongst student team members. We utilized a mass-email chain for communication amongst all individuals involved in the project. We also have a shared drive with an extensive directory containing our accumulated knowledge base, presentations, design documents, and eventually our designs. The Software team utilized our assigned Git Repository for the creation of their Digital Twin (discussed later). In addition, the Software team organized and attended weekly meetings to discuss softwa-respecific design problems. Finally, we had weekly 2-3 hour meetings with all associated members of the project to talk about the progress that we have made.

#### 3.2 TASK DECOMPOSITION

- Knowledge Acquisition: Reading papers, projects, journal, courses, etc. on quantum mechanics and computing. Can be broken into semi-distinct areas of research:

- General Quantum Mechanics Knowledge -<u>Mike and Ike book on Quantum</u>

- Quantum Computer Design <u>Client Provided State of the Art Review</u>, Honeywell and IonQ whitepapers, etc.

- Quantum Simulation and Design <u>IBM Quantum</u>, <u>QISKIT</u>, <u>Quirk</u>, more forthcoming

- Initial computer design: Decomposing this step was contingent on adequate understanding of quantum computing components. Substeps were:

- Defining Ion-trap Design

- Memory vs. Computation Traps

- Geometry Selection (2D linear, junctioned with trap inversion)

- Classical computer control systems

- Laser system controls (Classical implementation)

- Electrode controls (Classical implementation)

- Defining ancillary hardware:

- Number and makeup of ancillary components

- Base specific piece of hardware on (limited) qualifying characteristics

- Positions of components relative to chip and traps

- Laser Systems:

- Cooling: Doppler, Simulated Raman, Sideband

- Trap and ion Initialization

- Global Addressal

#### • Initial software digital twin simulation.

- Create architecture for program with the following ideas in mind

- Optimize scheduling to reduce noise and decoherence

- Make the architecture easily expanded upon

- Make architecture uphold to industry standard with functions that do one thing, are named well, and the architecture should be specifically made for the project

- Implement the following in code:

- Moving qubits for operations

- Scheduling qubits appropriately

- Node level functionality

- Noise reduction and error correction within these functions

- Quasi-crystal memory qubits

- Correctly take input gates and give corresponding output

- Create unit tests for software

- Unit tests will test each component. The test shall be specific and uphold to industry standards

- The tests will be run and shall be adhered to for future development, therefore a focus should be on quality

- Secondary computer design steps, in tandem with or contingent upon previous steps:

- Client functional review: Iteration of specific elements of hardware and software design

- Solidworks design of known hardware components (Chip and traps) for purposes of spatial reasoning

#### • Deliverable creation

- $\circ$   $\,$  Creation of figures and table to aid understanding

- Lightning Talk presentation creation

- Mid-Semester and End-Of-Semester presentations

- $\circ$  ~ Demo video of Digital Twin

- Drafting of End-of-Semester Reports

#### 3.3 PROJECT PROPOSED MILESTONES, METRICS, AND EVALUATION CRITERIA

# Due to the highly theoretical nature of our project -the construction of a quantum computer- , quantitative or physical milestones are difficult to create:

- Knowledge Acquisition

- This step was purely measured by relative knowledge

- Knowledge acquisition continued to be the primary step of this entire project, and extended from the first week of 491 through to the last week of 492

- A good yardstick to measure our success in this step was by our understanding of increasingly complex bodies of knowledge (increasingly complex papers)

- Around week 10 of CPRE 491, we reached a relative milestone, where our work becomes not solely knowledge acquisition based, and was simply performed as needed

#### • Initial Computer Design

- Nailing down specific elements of the quantum compute hardware design were important milestones

- Ion trap size

- Ion trap orientation on chip

- Number of and purposes of lasers used for addressal and computation

- Number of and purposes of ancillary hardware used for addressal and computation

- Location of laser producers / ancillary hardware relative to chips

- We did not end up having any metrics / evaluation criteria for the computer design (initial no secondary / further iterations) other than

- Does it fit in a reasonable packages

- Can all hardware components and lasers see elements of the trap / chip

- Within reason, is there any overlap in non-physical spectrums (primary concern was EM)

#### • Software

- Large software milestones, our software will have:

- The ability to optimize qubit operation sequences

- A full suite of unit tests

- The ability to simulate decoherence and noise

- Quasi-crystal memory qubits

- We will evaluate our software based on unit tests, with the following criteria in mind:

- Our output should have above a 99% fidelity

- Qubits must have enough coherence time to be used appropriately

- Qubits must be able to communicate necessary information with other qubits

- We must be able to scale our overall number of qubits to a kiloqubit level with our computer staying fully functional

- Non-objective measures:

- Our code shall be well abstracted

- Our code shall be well documented

- Our code shall be easily understandable

- Secondary computer design steps, in tandem with or contingent upon previous steps:

- SolidWorks design of known hardware components (Chip and traps) for purposes of spatial reasoning

- There were no specific goals of the SolidWorks design other than confirming metrics and evaluation criteria laid out in the Initial Computer Design section above

- The milestones that we achieved with the SolidWorks design was a schematic of the trap and a schematic of a single chip, both using simple polygons.

- Chip circuitry design This was not completed

- The only metric for this milestone was whether or not we could fit the circuitry on the chip, and due to work elaborated on later in the report, this metric was effectively met.

#### • Deliverable creation

0

- Rough drafts and final versions of all presentations

- 491 Lightning Talk presentation

- 491 End of Semester presentation

- 492 Mid-Semester Update

- 492 End of Semester presentation

- Rough draft and final versions of both reports

- 491 End of Semester report

- 492 End of Semester report

- Single (and subsequent if deemed necessary) takes of recordings

- 492 Mid-Semester presentation recording

- 492 End of Semester "How To" guide of the Digital Twin

- A milestone we did not achieve was the rough draft of a paper outlining our accomplishments for publication in a research journal. This was assigned to one team member at the tail end of the 492 semester by our research advisor, who did not give adequate time or resources considering other deliverables needed for this course

- Metrics and Evaluation Criteria for all deliverables are outlined in rubrics and culminated in grades given by advisors and judges of the CPRE 491 / 492 courses. These rubrics and grades will not be discussed in this report.

### 4 Design

The design is where the bulk of our work can be viewed. We start with looking at how our design fits into the broader context of quantum computing and the world in general. This has remained relatively unchanged since CPRE 491. We go on to discuss (briefly) the previous work and solutions in this field as well as the blatantly obvious technical complexity that accompanies designing a quantum computer. Part 4.2 dives into our design decisions and how we came up with / evaluated solutions. The final parts of this section dive into our specific design, any concerns and considerations regarding it, and our overall thoughts on what we've done.

#### 4.1 DESIGN CONTEXT

The design context dives into an overview of how the QC design affects various global-scale aspects, briefly touches on how it touches on and incorporates previous work done in the field, and highlights the technical complexities of the design and our project as a whole.

| Area                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Public health,<br>safety, and<br>welfare | Due to the purely theoretical and research-oriented nature of our design, it has minimal immediate impacts on public health, safety and welfare of people. The design is intended for students and faculty in the field of quantum computing / quantum physics, and stands to further the goals of the field. Down the line, it is our hope that quantum computers will be commercially viable and unlock a new paradigm of computing power for the general welfare. We believe we are doing our part in furthering this goal. Hopefully, our contributions to the field of quantum computing will enhance public welfare, as prior advancements in technology have.                                                                                                                                                                                                                                                                                      |

| Global, cultural,<br>and social          | The most significant impact of this project will be in global, cultural, and social areas. With this being a design of Iowa State origin, although our findings will be publicly available, the project stands to benefit Iowa State oriented individuals the most. Iowa State is very behind in the race for quantum computing power and the end goal of this project is to reduce that gap through further recognition of the school's efforts, increases in staff count and caliber in this department, and student engagement in the field. Doing so will increase the longstanding culture at Iowa State of ingenuity. As a team, we say "If the first digital computer?" While ambitious, there is a chance of global effects of our design. If our design works and performs as we intend it to, this could help the global field of quantum computing move forward. It could help open a door for the QC community into another school of design. |

| Environmental                            | Again, due to the purely theoretical and research-oriented nature of this design, the environmental impacts of it are negligible at the moment. A physical quantum computer of this specification would require a great amount of energy to run, similar to other Quantum Computers (QCs) of today. The power requirements and necessity of running the computer at 10 Kelvin would be significant relative to many other senior design projects. Our QC would utilize materials standard in other QCs, but procedures around obtaining such materials may still be harmful to society and the environment. This is not something we have much affect over, as we would not be constructing the computer, and as such, sourcing the materials.                                                                                                                                                                                                            |

| Economic                                 | Should this QC stay within the realm of a hypothetical design, the economic impact will be very minimal. We hope that our design will spur further ideation and design creation, further leading to the financial viability of quantum computers as a whole. If we begin to construct a physical QC, the economic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### 4.1.1 Broader Context

| impact will be more substantial, due to the requirement of designing such a cutting-edge machine. We couldn't do any sort of component production at lowa State and would have to outsource it to a DoE lab. Even still, our computer would most likely not be financially viable, and as such, not have any arge macroeconomic effects for us or associated parties. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| arge macroeconomic effects for us or associated parties.                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                       |

Table 1: Ramifications of our project

#### 4.1.2 Prior Work/Solutions

The Honeywell and IonQ Quantum Computers have been built, but they have very few qubits, and are therefore limited. Our design is similar in many regards, but designed for a great many qubits, around 1,000. The design has achieved this by arranging multiple ion traps together into a node, and said nodes will be arranged to make a cluster. Additionally, our design uses a special memory-type ion trap that allows qubits to last longer.

Our design will be more like the Honeywell H1 QC. Both use Ytterbium (Yb) ions for qubits, each use electrodes to keep them in an ion trap, and each use beams of lights/lasers to set, address, cool and manipulate them. The Honeywell QC cools its Yb ions using Barium (Ba), while the IonQ QC does not. The Honeywell QC physically moves its qubits around to have them interact with each other, whereas the IonQ computer transfers information using light and swap gates.

Source: AVS Quantum Sci. 3, 044101 (2021); https://doi.org/10.1116/5.0065951

#### 4.1.3 Technical Complexity

#### The complexity and scope of designing a quantum computer is apparent to us:

- The physics and mathematics of the operations inside a quantum computer are so complex (literally, they have a large focus on complex numbers, e.g. (a+bi,c+di)) that we have largely neglected them for the purposes of the design. We are treating ion-traps, a (relatively) extremely new and unproven design, to be a single, solid entity within our computer. Our computer will consist of a number of these ion traps in a specific layout to facilitate computing on a larger-scale than other QCs currently known in the public domain.

- Our problem was fundamentally an engineering problem the layout and rough construction of a Quantum Computer with particular attributes. This holistically encompasses many aspects of the engineering design process including ideation (see below), tradeoff consideration (technical and otherwise), and rough prototyping.

- Our Quantum Computer consists of ion-traps laid out in a novel design to accomplish basic computing responsibilities: mutilation and storage of data for multiple cycles. This is very similar to designing a traditional computer, but with an extra helping of mathematics and physics.

- The handoff of ions between traps relies heavily on particle physics

- The scope of our design problem is a kilo-qubit scale quantum computer a novel concept yet to be successfully created. Designs for QCs with 10s or low hundreds of qubits do exist, but haven't been implemented due to cost, material, or technology constraints. We intend on making this computer with current technologies and materials, which will definitely be a challenge. Pushing the boundaries of a new field with existing technology will prove to be a sufficient challenge.

#### The complexity and scope of designing a digital twin to a quantum computer:

- Why a digital twin is necessary:

- A digital twin is necessary to simulate our ideas without having to create new quantum hardware for every new idea or test.

- We will need to use our quantum computer in the future instead of the qiskit backend.

- It is necessary to use some sort of quantum backend simulation until we have our quantum computer.

- We must have a mastery of our libraries and code to create a digital twin.

- The complexities of creating a digital twin:

- There is a lack of libraries for what we are trying to create, there are no libraries for quantum scheduling or node level design, so we are having to create all of our own code for this.

- There is great complexity to many of our ideas such as quasi-crystal memory traps

- We were not given much time to implement many of the complex ideas

- Understanding what we are creating and how to create it can be difficult, taking a relatively large amount of time to get the correct resources and ask the right questions to our clients

#### 4.2 DESIGN EXPLORATION

The Design Exploration section highlights the thought processes and design decisions that we made across both semesters of senior design.

#### 4.2.1 Design Decisions

In the Design Decisions section, we look at each of the questions we had to address over the course of both semesters. As time passed, our decisions became more granular and specific, and many decisions we had to make were based on larger decisions made earlier in time.

#### 4.2.1.1 Design Decisions in CPRE 491

#### Number of clusters in the computer

- These are the largest layer of the QC. Depending on their role, the number of these may be important to not bottleneck the computer during operation. An adequate number of these is important to the "scale" aspect of our design, as multiplying these elements will quickly get our computer to the size we'd like it to be.

#### Number of nodes in a cluster

- These are the intermediate layer of the QC. Depending on their role, the number of these may be important to not bottleneck the computer during operation. The number of each of these in each computing node will set the upper limit of computations the computer could perform.

#### Number of traps per node

- These are the base layer of the QC. They serve a fundamentally different role than the larger two layers due to their importance to the physical operations of the computer. The number of each of these in each computing node will set the upper limit of computations each node unit could perform.

#### Function(s) of traps, nodes and/or clusters

- The decision to use all computing components as duplicates which do any one or number of functions would sway the number of each type of component needed to effectively perform computing operations.

# Physical orientation of traps relative to other traps, nodes to other nodes, clusters to other clusters

- The orientation of each component is of paramount importance with respect to the physical tradeoff of ions, ability to hold information for multiple machine cycles, and ability to use quantum computing effectively.

#### 4.2.1.2 Updates on Design Decisions in CPRE 492

In 492, the larger QC design team split into the Hardware and Software sections. Each team ran with different aspects of the design, and as such, encountered different challenges and had to make different decisions which largely didn't affect the other half of the team.

#### Decisions the hardware team made during 492:

#### Number and size of ion traps

- While the number of ion traps per node was something that was discussed and ultimately decided upon during 491, our team had to decide if that number was reasonable to fit onto a single chip that would be able to function.

#### Ion trap orientation

- While we made very small strides in addressing this problem in 491, a bulk of the thinking behind the manner in which the ion traps would be situated was done this semester. This was also largely affected by the number and size of ion traps on a chip.

#### Laser operations on ion traps

- In a similar vein to ion trap orientation, the exact operations that needed to be performed by lasers to ion traps / ions was a big question going into this semester. We had to figure out how many lasers would be used and along which plane would the lasers address their respective target.

#### Number of, size, and type of ancillary hardware needed for laser operations

- The laser operations being performed had to be accompanied by specific physical hardware components that are discussed in later sections. We assumed that such components may have been necessary for proper operation when we were entering the semester, but did not know for sure.

#### Orientation of laser producing modules and ancillary hardware

- Lastly, based on basically all previous design decisions we had to make, we had to tackle arguably the hardest question: Could we fit the laser producing module and ancillary hardware in / around the quantum computer in a feasible manner. The primary driver of this decision was whether or not the lasers / hardware could "see" what it needed to for proper computation.

#### Decisions the software team made during 492:

#### What software to create first:

- Deciding what software to work on first is very important due to the nature of not having much time to work. We created the fundamentally necessary classes and functions in order to have as much done as possible. There were more minor and complex things we could have implemented such as the quasi-crystal memory qubits. We chose not to implement

the memory qubits because it would have been very complicated and we wouldn't have been able to implement the scheduling or have as good of documentation.

#### What language to use:

- We started a program in C++ but we moved over to a python program in order to take advantage of the useful libraries. Qiskit is a python library and allows us to easily run simulations of our quantum circuits without having to program it ourselves.

#### How to structure the software architecture:

- We decided to base our architecture on the idea that we would be solving a scheduling problem. We created our classes in a way that allows us to have a class specifically dedicated to optimizing the scheduling of operations on qubits. Having separate classes based on different things allows for our code to be more easily understood and altered in the future.

#### How to schedule the operations

- There main concepts that the software team focused on are decoherence and noise. We tried to decrease the decoherence by using qubits as late as possible. This is counterintuitive to classical computing but qubits cannot be stored for long periods of time, meaning we want to use them as late as possible. When qubits are moved, there is noise involved and so ideally you want to move qubits next to each other, then start the operations. We want to limit decoherence and noise because they decrease the fidelity of the computer, which is essentially how accurate the computation was. If fidelity is low, computations will fail.

#### 4.2.2. Ideation

The Ideation section outlines how we contemplated different solutions to a problem. In our fall semester (CPRE 491), we only dealt with one issue. We spent multiple weeks thinking of different potential solutions and evaluating each option before moving forward. In our spring semester (CPRE 492), each team dealt with multiple issues and quickly iterated through each problem with our first proposed solution.

#### 4.2.2.1 Ideation in CPRE 491

During the first semester, we had to decide upon the physical orientation of traps relative to others. As previously mentioned, the orientation of the ion traps relative to other ones is fundamental in the handoff of ions between traps, a crucial standpoint of our design and the driving force behind our scalable, modular design.

#### - Square Grid design with upper and lower tracks

- This was the design recommended by the advisors of our project. This type of design is supported by modern, 2-level wafer electronics printing and was what we ended up moving forward with. Similar to a street-level grid used in many newer towns, a meeting point would consist of two, three, or four "roads" (ion traps) converging in "intersections." This design calls for explicit usage of the cardinal directions to maintain order

- Tree design

- Two major factors permeate our design requirements. Firstly, the addition of ion traps at their intersections introduces additional noise and uncertainty, as a qubit traveling from one to another is less likely to go in the intended direction.

Secondly, the movement of a qubit reduces its coherence time, and introduces error into the QC. Therefore, we would do good to minimize both the number of ion traps at each junction, and the distance between each qubit. A tree-like design, such as a binary tree, compromises between these constraints. It allows for each qubit to only need to travel  $O(\log(n))$  ion traps to get to any other qubit, as opposed to a line or circle, which requires O(n) ion traps to be traversed. It also requires less ion traps per junction between ion traps than a grid or wheel spoke. Even if the design is not strictly a tree, it can have aspects that are like one.

#### - Wheel and spoke design

This was a design thought of by a team member. It involves many ion traps converging at a central point, where ions could be handed off to any one of the number of "spoke" ion traps. Around the outside of these spoke traps, we could have a "wheel" of ion traps providing a potentially different function.

#### - Triangular grid design with upper and lower tracks

- This is a slightly different iteration of the grid design. Instead of having squares, we could have a triangular grid, with each connection being a meeting point of three ion traps instead of two or four. This design would not use the cardinal directions, and all intersections would have exactly three connections (outside of those on the corners of the grid).

#### - Other 3+ Layer designs

This is a subset of thoughts that we came up with when considering the binary tree design. This school of design requires the practical capability of electronics manufacturing with 3+ layer wafer design. We did not look much into this option, as to our knowledge, such wafer design is not possible.

#### 4.2.2.2 Updates on Ideation in CPRE 492

As mentioned in 4.2.1.2, the Hardware and Software sections of the design diverged in 492. Each team ran with different aspects of the design, and as such, encountered different challenges and had different ideas on how to overcome them. We dealt with multiple separate problems and usually did not come up with multiple options for each decision, but ran with our original choice unless we needed to redesign it. We also had to be slightly more conscious of how our ideas may affect the other team, which we briefly address in the tradeoffs section.

#### Hardware Decisions:

#### Number and size of ion traps

- For 492, we continued to run with our previous idea for number of traps per chip (specifics in 4.3)

- For the size of the ion traps, we initially passed our design off of the HOA (High Optical Access) trap's measurements. This is the only public ion trap design to our knowledge.

- Near the end of 492, we were informed the HOA trap would not be able to perform the ion handoff due to how the electrodes were set up. With no other publicly available trap designs, we were forced to move forward with the HOA's measurements as a "proxy" for what an actual trap should be, size-wise.

#### Ion trap orientation

- when we were thinking about how to arrange / orient the ion traps on the chipo, we went for a layout that maximized the distance between any two ion traps regardless of if they were on the same chip (ie the above chip or the below chip)

- A big deciding factor was how to orient the traps so that they could be addressed by various lasers. having some part of the trap near the edge of the chip and at a right angle relative to the chip was very important.

#### Laser operations on ion traps

- There wasn't as much traditional "ideation" involved in this decision, but moreso referencing proper papers and consulting with our advisors about what needed to be done to get the computer ready for / actually doing the computation. Our PhD student, Gavin Nop, was particularly helpful here.

#### Number of, size, and type of ancillary hardware needed for laser operations

- Similar to the previous, referencing the proper academic resources was how we came up with our 'solution' to this challenge.

- Our solution for this is much less specific than any other challenge. This is because no paper goes in depth into the specifics of the ancillary hardware, and all of our advisors have never seen a real quantum computer (as such, don't know the ancillary hardware we would need). We were able to piece together an idea of what we needed / roughly how many of each thing we would need, but not the make and/or model of the ancillary hardware used in similar quantum computers.

#### Orientation of laser producing modules and ancillary hardware

- This was the truest "ideation" process we had to undertake. This was the last design challenge we worked on, and we don't have a great solution due to how late we undertook this. The requirements were pretty open-ended, so much so that there were various solutions that we didn't even think of initially.

#### **Software Decisions:**

#### What software to create:

- There was not much change in ideation of what software would be as it was only mentioned a few times in 491. The nature of this project is that we are creating things without much guidance due to it being very "ground level". The graduate student associated with our project in 491 created a physics simulation for keeping qubits in ion traps and executing static handoffs. We decided to not work further along this due to the expertise required. When considering our client's broad goal: a digital twin that addressed any and all implementation concerns possible, we knew we had to limit the scope. Our software team decided to solely focus on the digital twin as a compiler and "executor" of quantum algorithms respective to our model of the hardware. It has many benefits, as it allows us to simulate the high-level concepts that are unique to our design, and it can be extended to greater depth and interfaced for use with the hardware in the future.

#### **Scheduling Policy:**

- By the time our team had a clear view on what the issue our client wanted us to solve was, we had limited time, and many implementation options available. To create a true optimization for the scheduling of quantum operations would have required both the

acquisition and application of a substantial amount of technical knowledge: more than we had procured in the previous semester. As such, we identified 3 possible policies that attempted a very low-granularity treatment of our quantum-computational concerns: as-late-as-possible, as-close-as-possible, and as-fast-as-possible. Barring some lengthy details of each implementation: our team collectively discussed and ran through a shortlist of hypothetical small-algorithm executions under each paradigm, and after consultation with our client, determined that the as-late-as-possible paradigm would yield the highest performance on average, and be most relevant to more optimal scheduling policies that could later be implemented as extensions/modifications of the ALAP policy.

#### 4.2.3 Decision-Making and Trade-Off

The methods in which we evaluated each solution differed greatly between semesters due to the number and variety of problems we faced. We faced a singly, impactful decision during CPRE 491, leading to us contemplating multiple designs thoroughly. During the spring semester, we placed less emphasis on ideation and more emphasis on speed, leading to less trade-off analysis and overall less time spent in the decision making phase.

#### 4.2.3.1 Decision-Making and Trade-Off in CPRE 491

#### Physical Layout of computer

- Grid design with upper and lower tracks

- Pros:

- Moderate junction density, at most 4 for a square grid

- Cons:

- Moderate-High  $O(n^{(1/2)})$  distance between qubits

- Tree design

- Pros:

- Moderate-low O(logn) distance between qubits

- Moderate-low junction density, at most 3 in the case of a binary tree.

- Principles of the tree design may be applied to other designs.

- Cons:

- Leafs have the worst travel time, and they are the most prevalent.

- Other designs have better qubits distance or junction density individually

#### - Wheel and spoke design

- Pros:

- Low distance between qubits

- Low junction density on the wheel, 2 or 3 ion traps per junction.

- Could support parallel computing in multiple "spoke" ion traps

- Cons:

- High junction density, particularly in the center of the wheel

- Ions could get lost in the hub of the wheel, where the spokes all meet

- Triangular grid design

- Pros:

- Moderate-Low distance between qubits.

- The structure would be most dense, and take up less space.

- Cons:

- High junction density, at most 6 for a triangular grid

- Other 3+ Layer Designs

- Pros:

- Denser, taking up less space.

- Vertical traversal allows for shorter qubit traversal time.

- Cons:

- Likely high junction density

- Probably not possible with current technology

We have not yet made an official decision on this or other considerations yet, as knowledge acquisition is still underway to help more thoroughly inform our decisions.

#### 4.2.3.2 DECISION-MAKING AND TRADE-OFF IN CPRE 492

In 492, we placed less emphasis on ideation, and thus, less "tradeoff analysis" was done. We placed more emphasis on workable solutions due to the larger number of decisions that needed to be made. Most of the time, we would move forward with our initial design and only come back if there was a critical flaw.

The hardware side only had two scenarios where we had to decide between 2+ workable solutions: **Ion trap orientation**

- Our initial design called for not having the wirebond section of the ion traps close to each other regardless of plane. We did this because we believed this would minimize the chance of any of the 30+ wire bonds on each trap from getting tangled with each other.

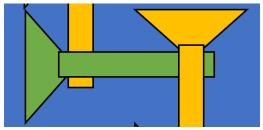

Figure 1: Example of initial ion trap orientation

- Later on, we decided that a more uniform design with all wire bond sections located as close to the edge of the chip was preferable. We came up with this by thinking on a more global scale, and it turned out having most of the wires and circuitry located around the outside of the chip made it easier for circuit design and meant we could get significantly outsized returns to cleanliness by making the chip just a little bigger.

#### Orientation of laser producing modules and ancillary hardware

Designed that were considered included:

- Hardware located in-plane and close to chip

- Scrapped because ancillary hardware was deemed too large to fit close to the chip

- Hardware located in-plane and far away from chip

- This was (and still is) a viable design for our computer, but would be slightly harder to work on set-up wise due to the still relative closeness of our ancillary hardware compared to our design we selected

- The fact that everything is on the same plane is both the pro and the con of this option, as it makes it slightly easier to work on but means that there is slightly more congestion and a higher chance of unintended overlap.

- Hardware located out-of-plane and far away from chip

- This is our current solution. We discovered that it doesn't really matter where the ancillary hardware is on the X, Y, or Z plane, so long as the lasers nearby the ancillary hardware could be directed to a right angle relative to the chip via mirrors. The ancillary hardware could be arbitrarily large so long as the laser lengths emanating from our ancillary hardware / laser producing cluster were arbitrarily long.

- As Nick put it "The ancillary hardware could be the size of a building if each laser were just 5 miles long."

- The pro of this design is the aforementioned arbitrary size limit on ancillary hardware, while the con is that ancillary hardware may be located non-optimally for lab work.

- Non-ion-trap software backend

- The quantum computer that our backend runs on is not an ion-trap. It would have cost money in order to get the ability to use IonQ, our only option. We decided it wasn't worth the cost to have a more realistic backend. One of the main factors is due to the fact that we are using the Qiskit library, we wouldn't be given more functionality and we wouldn't be able to move qubits or do our own scheduling. Overall we decided the slightly more realistic simulation would not be worth the cost.

#### - Degree of Implemented Scheduling Policy Optimality:

As discussed in a previous section, the requirements for implementing a fully robust quantum scheduler were beyond our capacity. In its place, we opted for a policy we referred to as "as-late-as-possible", which placed the highest priority on completing operations on a given qubit as close to its measurement as possible. This won out over policies that grouped operations utilizing the same qubit as close as possible while maintaining a conflict-serial schedule, and those which prioritized getting all qubits to their final state as quickly as possible. This was the result of a consultation with our client, from which we concluded that this would have the greatest impact on average. It was also relatively simple to implement, and will provide a more effective baseline for generating conflict-serializable schedules to be used by a more robust scheduling optimizer that more faithfully addresses quantum mechanical concerns in the future.

#### 4.3 PROPOSED DESIGN

The bulk of our project lives in the Proposed Design section. This section explains the design of our quantum computer, starting with an overview dating back to the end of CPRE 491 and then delving into how it works and modifications that were made during CPRE 492. We finish off by discussing areas of concern both past and present.

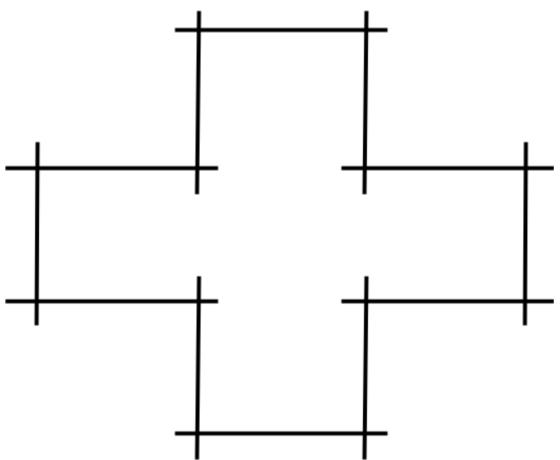

Figure 2: A brief overview of the shape of our RF ion trap design

We have designed a quantum computer schematic. Pictured above is our design for a node of this computer. This node will be composed of 12 ion traps, and each will hold ~10 ion. Each ion acts as a quantum bit ("qubit"). Each of these nodes operate in the same fashion, and connect to each other via a currently unknown method. This is the paradigm of a different Senior Design team and wasn't within the scope of our project.

To transfer information within a node, qubits continuously move between ion traps at junction points near their ends. Due to the state of current technology in the field, it is best to implement junctions between two ion traps with a right angle. The part of each ion trap that extends past this junction helps to guide the qubit to its destination. Additionally, the ends of each ion trap contain a DC voltage stop - a wall that stops ions from flying off the ion trap. The cross design is composed of only right angle junctions, and is, to some degree, symmetric, so forces from electrodes will cancel each other out, which is desired.

#### 4.3.2 Detailed Design and Visual(s)

We have designed a quantum computer schematic. The central part of the computer is a node, which itself is a quantum computer holding a number of qubits on the order of ~100. The node will be used in clusters to build a quantum computer of many clusters, which in total can hold on the order of 1000 qubits.

A "qubit" is a quantum bit in a superposition between o and 1. A single qubit may be represented as a vector of two complex numbers, the magnitudes of each are the probabilities that the qubit will be either o or 1 once it is measured, so the magnitude of the magnitudes of the elements of the vector is always 1. Qubits may be manipulated by quantum gates, which may be thought of as unary matrices, that is, any matrix when multiplied to its conjugate transpose becomes the identity matrix. This allows the probabilities of a qubit being o or 1 to be flipped, or for the polarity of one of the aforementioned complex numbers to be flipped, or for a qubit to gain an equal probability of yielding o or 1, from a state of exactly o or 1, but do nothing when applied twice. There are also two-qubit gates, such as the controlled not gate, which flips one qubit's value if and only if the other will yield 1 when measured. This allows for quantum entanglement, a situation where one qubit will not yield a different result than another qubit will when the same outside stimuli are applied to both. Complex quantum algorithms take advantage of these qualities to perform tasks faster than on digital computers. Though the complex numbers cannot be measured directly, their magnitudes can be measured by running the same algorithms multiple times, and measuring average responses.

As stated prior, qubit information is stored in Ytterbium cations, which are called "physical qubits." The last valence electron in the Ytterbium cation exists in a superposition between its usual orbital, and an excited state, allowing for us to use the ion (electron) as a qubit. Multiple physical qubits may be used together to model a single qubit with greater accuracy, called a logical qubit. We use lasers to emit photons, which then impart the Ytterbium atom with energy depending on the wavelength, as the last electron can absorb the incoming light, and jump to a higher state. Depending on the frequency of light provided, the electron could jump to a specific unstable state, and then go back down to its usual position. This allows us to set specific qubits to be either o or 1. Furthermore, we can measure the orbit of the electron by sending light to it, and then measuring what we get, because some light may be absorbed by the ion and will not go through it. Using these lasers, we can set and access the qubits.

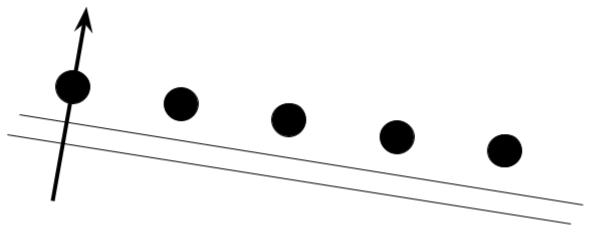

In order for the qubits to be useful, the ions must exist at a very low temperature; otherwise, there will be too much noise, and the physical qubits we do have will retain information for less time. This temperature must be around 10 - 12 Kelvin for the computer to operate. Therefore, we will employ multiple methods of cooling, including doppler cooling and passive Barium cooling. In doppler cooling, we emit light at a specific frequency to cause the Ytterbium ion to lose energy and slow down. In passive Barium cooling, we place Barium ions between the Ytterbium ions, and then cool the barium ions more aggressively, which then cool the Ytterbium ions. The image below depicts an ion gate with ions, and a beam of light going from the top to the bottom.

Figure 3: Ions suspended above an ion trap

Useful quantum algorithms are complex, and require many qubits to execute. Therefore, our machine utilizes many qubits, on the order of 1000, to advance the field of quantum computing. The primary challenge to accomplishing this feat is that qubits are very unstable, and exist for only a short amount of time. Usually, the addition of more qubits in a quantum computer introduces noise, and reduces the amount of time a qubit can hold accurate information. Therefore, we use special memory-specific ion traps that are designed to only store qubits without doing gate operations on them. This is a key point where our design diverges from existing designs.

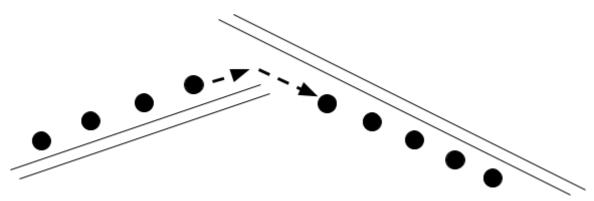

Figure 4: Visualization of an ion handoff between two ion traps

In addition to using memory specific ion traps, we also use a vertical transfer, shown above. In this, qubits will transfer from one ion trap to another vertically, just hovering across. We expect that this will limit the noise that a qubit encounters while traversing ion traps.

#### 4.3.3 Updates to Detailed Design and Visual(s)

In 492 we updated the design on the hardware front and essentially started the design on the software front. Challenges and ideas for each element of our design can be found in previous sections, as 4.3.3 will only cover the product of our labors. The hardware portion will have substantial visual references in this section, whereas software will be heavier on the explanations. The code used is at the bottom of this report.

#### Hardware Design:

Ion trap size

- The ion trap measurements we went with were exactly those of the HOA trap. As previously mentioned, these are being used as a proxy due to the HOA trap's inapplicability to our specific design.

- We also discovered that components called the "Spacer" and "Interposer" need to be placed below the actual ion trap for proper functioning.

Figure 5: A measurement-based schematic of a single HOA ion trap

Figure 6: Side profile of the quantum computer. Purpose of yellow and green traps addressed in following section

#### Ion trap orientation

- Again, this was largely decided upon prior to 492. We moved forward with our cross based design. In 492, we also updated the design by standardizing the location of our RF addressal pads. Now, each addressal pad is facing outwards from the center, towards the edge of the chip. This makes it easier to implement the wiring necessary for this circuit. We also elongated each track, just so every component is able to fit on our wafer. This was one of the main takeaways from the Solidworks design.

- In the following image, the green traps represent those on the upper wafer, and are memory traps. The yellow traps represent those on the lower wafer, and are computational traps.

- Based on the sizes of the ion traps decided upon in the previous step, we decided a chip size of 26mm would be ample.

Figure 7: A top-down view of the central quantum computer, with top chip removed for easy viewing

#### Laser operations on ion traps

- Using academic resources and professional guidance, we deduced we would require the following lasers with the following purposes:

- Two Barium Doppler Cooling Lasers, one with a 649.9nm and the other with a 493.5nm wavelength

- These lasers will be prevalent during initialization and intermittently

- Cooling lasers are not used at the same time as actual computation

- Two Yb ionizing lasers: 369.5nm & 398.9nm wavelengths

- These lasers are used once per trap to ionize the Yb atoms, used before any other lasers

- The 369.5nm laser is also used for readout of ions

- Two Yb Optical Pumping lasers are needed, with 369.5nm & 935.2nm wavelengths

- These are used intermittently through computation to reset ion values

- One Addressal laser of unknown wavelength

- This laser will be shot "at the side" of the ion trap, in a manner that it can view the entire region of the trap that holds ions. This contrasts with all other listed lasers, which will be shot "down" the ion trap.

#### Number of, size, and type of ancillary hardware needed for laser operations

- Some operations performed before / during / after computation require lasers to be fire through pieces of hardware. The main two piece of hardware are Acousto-Optic Modulators (AOMs) and Electro-Optical Modulators (EOMs). The purpose of these pieces of hardware are not discussed in this report and weren't particularly relevant for us,

- A serious challenge was the non-specificity of the exact type of each piece of hardware needed. AOMs and EOMs come in all sorts of shapes and sizes, and no one knew what differentiated one type from another on a basis relevant to our project, even our professional guides.

- The 493.5nm Barium Doppler Cooling laser is run through a sequence of two AOMs

- Both Yb Optical Pumping Lasers are run through separate EOMs

- The Global Addressal laser will need to be run through some sort of diffractor to be able to reach all areas of the ion trap, as well as an AOM

- All measurements of AOMs and EOM were used as aggregates of sizes pulled from datasheets of various components. These dimensions are more ballpark figures than in reference to any specific piece of hardware.

Figure 8: A cutaway view of all lasers and ancillary components that will need to feed into the ion

#### Orientation of laser producing modules and ancillary hardware

- The last issue was tackled was where to position the lasers and hardware. We decided to use reflectors and position all ancillary components arbitrarily far away.

- Depending on which direction the RF addressal pads of the ion trap face, and which chip the ion traps are on (upper or lower), we positioned the reflectors to point upwards or downwards from the chips' plane.

- Yellow squares are meant to reflect the lasers from a position above the chips, whereas orange squares are meant to reject the lasers from a position below the chips .

Figure 10: Top-down view of reflectors and lasers. Top chip removed in graphic for better viewing.

Software Design:

Figure 11: UML Diagram of Digital Twin

#### Overview

#### **Functionality:**

- We optimize execution of a quantum circuit by:

- Simulating circuit execution in our hardware design

- Taking advantage of parallel processing

- Accounting for necessary Qubit movements

- Integrating with Qiskit backends

#### **Target User:**

- Future project developers/maintainers

- Developed as a library, our software is supposed to be a backend

- Users specifically trained in how to use our software

- We do not need to make our code accessible to people who have no knowledge of our project. This allows us to not create UI's and use technical language throughout our project.

#### Substance - Three Classes:

- Node class: The Node class is given a sequence of instructions and computes a dependency mapping between operations and resources. It constructs cycles to be used in the NodeLiteral class.

- Node(n): Constructor

- sop(q,op,ph): Single-qubit operation

- Supported gates: x, y, z, h, p

- mop(p,q): Multi-qubit operation (C-NOT Gate)

- describe(): Prints a description of the node

- getLiteral(): Generates a NodeLiteral from the current Node object

- Cycle class: The cycle class simulates a cycle of a quantum computer cycle

- Cycle(n): Constructor

- sop(p,op, ph): Single-qubit operation

- mop(p,q): Multi-qubit operation (C-NOT gate)

- mvq(p,q): Qubit movement: Swaps two adjacent qubits

- describe(): Prints a description of the Cycle to stdout

- **NodeLiteral class:** The NodeLiteral class simulates the hardware level node, it directly interacts with qubits, there are no optimizations or controls here

- NodeLiteral(n): Constructor

- addCycle(cycle): Adds a Cycle: a list of operations to do in a machine cycle

- describe(): Prints a description of the NodeLiteral to stdout

- setOrder(order)/getOrder(): Assigns/returns logical qubits to initial locations

- getcirc(): Generates and returns a Qiskit QuantumCircuit

- execute(backend): Executes on a Qiskit backend

```

Make A Node

= Node(8)

n.sop(0,'x')

n.sop(1,

n.sop(0,

n.sop(2,

n.sop(2,

n.mop(0,3)

n.sop(0,'p',.5)

# Print Description To Validate

print("NODE DESCRIPTION")

n.describe()

# Generate NodeLiteral

l = n.getLiteral()

# Print Description To Validate

print("NODELITERAL DESCRIPTION")

l.describe()

# Generate Circuit To Validate

circ = l.getcirc()

print(circ.draw('text'))

# Generate And Execute A Circuit For Validation

backend = BasicAer.get_backend('qasm_simulator')

r = l.execute(backend)

print(r.get_counts())

print("END PROGRAM"

```

Figure 12: Software example user code

#### 4.3.4 Past / Present Areas of Concern

The silver bullet of our design lies in its nature - it is simply a design. Until a real computer that's based on the hardware of this design is constructed, we will never know if our design works. To that end, some of the most important factors of our design thus far may not even work, which we refer to later in 4.5 Design Analysis. Further development on our design will be largely dependent on access to high-grade electro-dynamic simulations, a probable precursor to building the actual computer. With our existing simulation software, we can not be sure that the results of our simulations accurately represent a real world outcome. We must be certain that under scrutiny from more well-endowed individuals and institutions with access to more advanced modeling software, our design holds up.

#### Hardware

On the hardware side, we have broad areas of concern around the feasibility of production of this design. This was something that we were concerned with at the outset of 491, but as we've made design decisions and had to "hand-wave" some of the details of this design away due to lack of

publicly available knowledge, these concerns have become ever more present. Specifically, the fact that we don't have an exact ion trap to base this design off of is cause for great concern. Knowing that the single public design for an ion trap can't be applied to our design means that the exact dimensions of a viable ion trap are up in the air. Additionally, there are minor concerns around ancillary hardware. No one on our team nor none of our advisors have seen a quantum computer, so the size and number of ancillary hardware was backed into based on tangential writings of people who have seen a QC "in the wild." We think that our design more or less solves this problem by locating ancillary hardware some distance away from the trap, but until a computer based on our actual design is constructed, we just don't know.

#### Software

There are many concerns with creating a digital twin to a quantum computer. We need our code to be compatible with other teams. There is a team creating a cluster level digital twin and if we create incompatible code then it would be a major setback in the future. Software is only as useful as it is in the real world. There are reasons why companies choose to create slower code that is more abstracted. It is incredibly important to have code that can be expanded upon and is understandable by others. If our code cannot be understood then it will become completely useless as soon as someone tries to expand upon it. Our code must be accurate in testing what our hardware team wants to implement otherwise we may test one thing and end up with inaccurate results.

#### 4.4 TECHNOLOGY CONSIDERATIONS

Our design for a quantum computer is made out of one modular component - a Ytterbium ion-trap. While a fairly recent development within the broader scope of computing, this is a tested way of performing computational operations. These ion traps have two segmented RF electrodes with DC voltage steps that create a "tube" above the trap that the ion sits in.

While our initial design used the High Optical Access (HOA) trap outlined in a 2016 paper from Sandia Labs, we discovered at the end of the semester that this ion trap does not support the kind of "ion handoff" that is a fundamental part of this computer's operation. Designing a new ion trap is well outside of the scope of this class, so we moved forward using the HOA as a basis for measurements of this design.